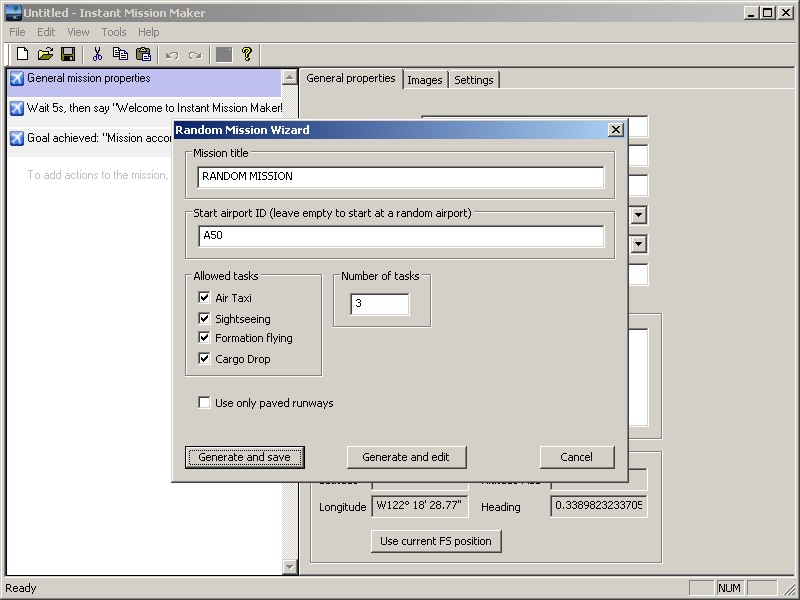

After substantial pre- hardware optimization steps, the necessity of hardware implementation for bottleneck code in the PC environment became evident and solvable beginning with the methodology described in, , and implementing a novel methodology for this specific application. It was interesting to examine the gains and losses in performance on the new platform, as well as unexpected observations before implementing hardware. In order for the hybrid system to run, the IDL software was modified to account for platform differences. The solution involves converting the application to a PC/Windows/RC platform, selected mainly by the availability of low cost, adaptable high-speed RC hardware.

This paper describes these steps for the GOES-8 application, a software project developed using Interactive Data Language (IDL) (Trademark of Research Systems, Inc.) on a Workstation/UNIX platform.

However, since this technology is still maturing, intensive pre- hardware steps are necessary to achieve the benefits of hardware implementation. It has been shown in and that this configuration can provide superior inexpensive performance for a chosen application on the ground station or on-board a spacecraft. The solution is based on a Personal Computer (PC) platform and synergy of optimized software algorithms and re-configurable computing hardware technologies, such as Field Programmable Gate Arrays (FPGA) and Digital Signal Processing (DSP). Although large super-computer facilities are the obvious heritage solution, they are very costly, making it imperative to seek a feasible alternative engineering solution at a fraction of the cost. This paper proposes a solution to a related problem for the Geostationary Operational Environmental Spacecraft (GOES-8) image processing application. Spacecraft telemetry rates have steadily increased over the last decade presenting a problem for real-time processing by ground facilities. Hestnes, Phyllis Jentoft-Nilsen, Marit Petrick, David J. Pre- Hardware Optimization of Spacecraft Image Processing Software Algorithms and Hardware Implementation We review the hardware and software status of QCDOC and present performance figures obtained in real hardware as well as in simulation. The first ASICs became available in June of 2003, and the testing performed so far has shown all systems functioning according to specification. This strong scalability, together with low power consumption and a price/ performance ratio of $1 per sustained MFlops, enable QCDOC to attack the most demanding lattice QCD problems. This ASIC was custom-designed so that crucial lattice QCD kernels achieve an overall sustained performance of 50% on machines with several 10,000 nodes. QCDOC is a massively parallel supercomputer whose processing nodes are based on an application-specific integrated circuit (ASIC). Salapura, Valentina Wisniewski, Robert Wīoyle, P. A state machine receives the signal and selects a configuration register from the plurality of configuration registers for reconfiguring the one or more performance counters. A plurality of configuration registers stores a set of performance counter configurations. A storage element stores data value representing a time interval, and a timer element reads the data value and detects expiration of the time interval based on the data value and generates a signal. Hardware support for software controlled reconfiguration of performance counters may include a plurality of performance counters collecting one or more counts of one or more selected activities. Salapura, Valentina Wisniewski, Robert W. Hardware support for software controlled fast reconfiguration of performance counters

0 kommentar(er)

0 kommentar(er)